They build higher-level cells by using these leaf cells. At the same time, circuit designers are designing optimized circuits for leaf-level cells. Logic designers decide how the design should be structured by breaking up the functionality into blocks and sub-blocks. Design architects define the specifications of the top-level block. Typically designers use these two approaches side-by-side to construct complex circuits.

FULL ADDER VS HALF ADDER TRUTH TABLE FULL

E.g., you have two half adders available, and you can construct a full adder using these two half adders. half adder.īottom-Up Methodology: In this approach, we first identify small blocks that are available to us and use them to construct a big block. you want to construct full adder, so you immediately identify two small blocks i.e. We further divide the small block to leaf cells which cannot be further divided. Top-Down Methodology: In Top-Down we first identify or define the big circuit or big block and then identify a small block used to make this big block.

FULL ADDER VS HALF ADDER TRUTH TABLE CODE

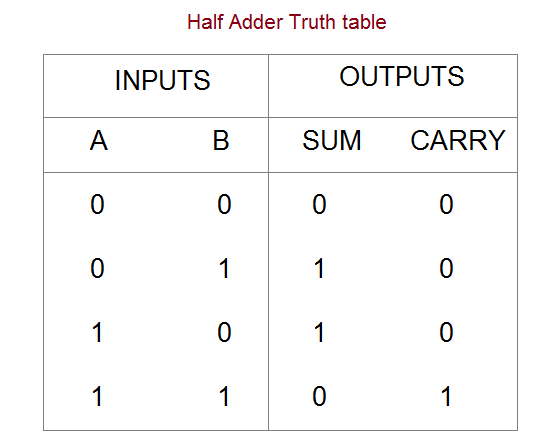

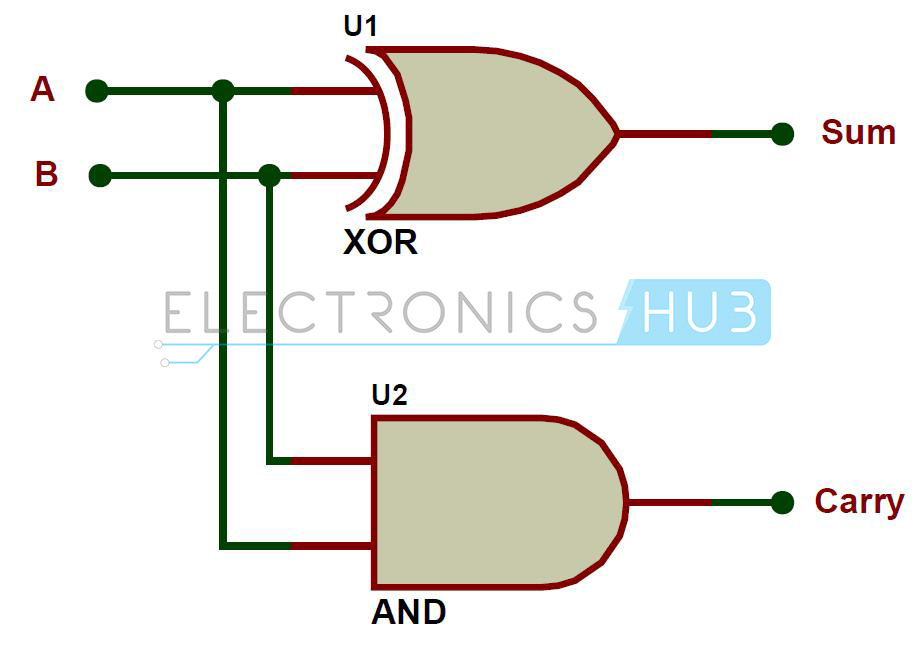

There are two design approaches when writing code in hierarchical style to divide the big complex circuit into smaller modules and further dividing these modules to even smaller modules like gates etc. The key idea is to divide and conquer i.e. Hierarchical Designing: A Hierarchical methodology is used to design simple components to construct more complex component. This tutorial will further provide some examples and explain why it is better to code in a hierarchical style. In “ Introduction to Verilog” we have mentioned that it is a good practice to write modules for each block. Just drop in a comment in the comments section below.This tutorial focuses on writing Verilog code in a hierarchical style. So using that syntax, we will assign the inputs to the output vector as follows: O A, O => O) Įnd tb RTL Schematic Half and full adder(together)-RTL Simulation Waveform Half and full adder(together)-waveformĪs always, if you have any queries, we would love to address them. We saw the syntax for the when-else statements in our post on the dataflow architecture. Port ( A : in STD_LOGIC_VECTOR (2 downto 0) Īrchitecture dataflow of FULLADDER_VIATRUTHTABLE isĭataflow architecture has when-else statements that are very handy when coding with truth tables. And generally speaking, when we are dealing with multiple inputs of the same kind, using vectors saves us a lot of complexity. The first one will be the SUM, and the second one will be the CARRY. And the output vectors will have two slots. We can easily assign two vectors, one to inputs and one to outputs. The reason is that since we are using the truth table of the full adder, we have three inputs and two outputs. We will declare the entities as vectors.īut why? Why not declare each input/output separately? The entity-architecture declaration for the VHDL code of a full adder will have only one difference. Since this carry is not added to the final answer, the addition process is somewhat incomplete. The half adder gives out two outputs, the SUM of the operation and the CARRY generated in the operation.

Explanation of the VHDL code for half adder using its logic equation and the dataflow method.Logic equation and logic circuit of a half adder.

0 kommentar(er)

0 kommentar(er)